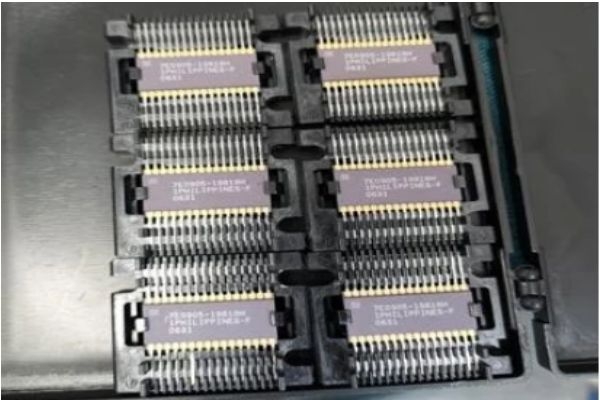

Xilinx、Altera、Lattice的FPGA器件都是SRAM查找表結構。Xilinx支持模塊化動態部分重構的器件族有XC6200系列,90nm工藝Spartan-3和Virtex-Virtex-II-E和Virtex-IIPro[7]。Acmel公司的AT6000系列同樣基于SRAM結構,只是SRAM的各單元能夠單獨訪問配置,即支持部分重構。Lattice公司的基于Flash的FPGA通過在Flash上存儲多種邏輯功能的配置數據流,經過配置實現不同邏輯功能,嚴格意義上講屬于靜態可重構技術。Altera公司的Flex系列、ACEX、APEX、Cyclone系列也是基于SRAM的可重構邏輯。

支持重構的FPGA器件有數量逐漸增加的趨勢。但目前價格相對偏高。由于可重構系統的研究歷史很短,目前尚未形成標準的結構形式,在此僅根據已有的應用做初步分析。按重構的粒度和方式,可重構系統可以粗略地分為兩種。一種是粗粒度重構單元的模塊級重構,即重構時改變某一個或若干個子模塊的結構。此時不僅電路邏輯改變,連線資源也重新分配。重構所需的電路輸出配置信息事先由編譯軟件生成。通常重構時系統需要暫停工作,待重構完成后再繼續。這種重構系統設計簡單,但靈活性不足,且有時不能完全發揮出硬件運算的效率。較適合應用于嵌入式系統中。另一種細粒度的重構單元的元件級重構,即重構時僅改變若干元件的邏輯功能。通常情況下重構時連線資源的分配狀況不作修改。

支持重構的FPGA器件有數量逐漸增加的趨勢。但目前價格相對偏高。由于可重構系統的研究歷史很短,目前尚未形成標準的結構形式,在此僅根據已有的應用做初步分析。按重構的粒度和方式,可重構系統可以粗略地分為兩種。一種是粗粒度重構單元的模塊級重構,即重構時改變某一個或若干個子模塊的結構。此時不僅電路邏輯改變,連線資源也重新分配。重構所需的電路輸出配置信息事先由編譯軟件生成。通常重構時系統需要暫停工作,待重構完成后再繼續。這種重構系統設計簡單,但靈活性不足,且有時不能完全發揮出硬件運算的效率。較適合應用于嵌入式系統中。另一種細粒度的重構單元的元件級重構,即重構時僅改變若干元件的邏輯功能。通常情況下重構時連線資源的分配狀況不作修改。